Accelerator for a read-channel design and simulation tool

Abstract

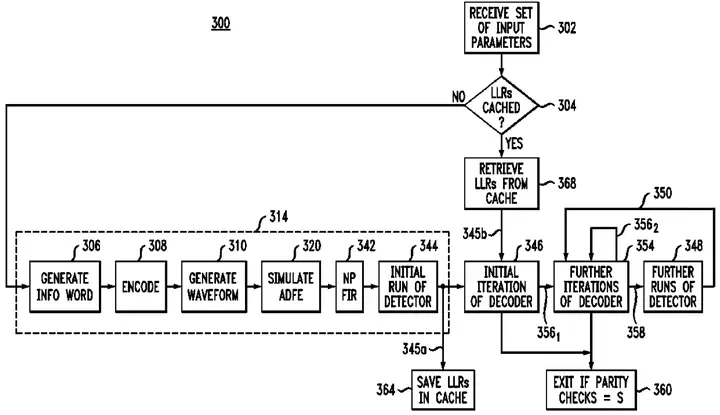

A computer-aided design method for developing, simulating, and testing a read-channel architecture to be implemented in a VLSI circuit. The method uses a coset operating mode and nonzero-syndrome-based decoding to accelerate the simulation of the read-channel’s error-rate characteristics corresponding to different parity-check matrices employed in the read-channel’s turbo-decoder, such as a low-density parity-check decoder. The acceleration is achieved through recycling some previously generated log-likelihood-ratio values, which enables the method to sometimes bypass certain time-consuming processing steps therein.

Type